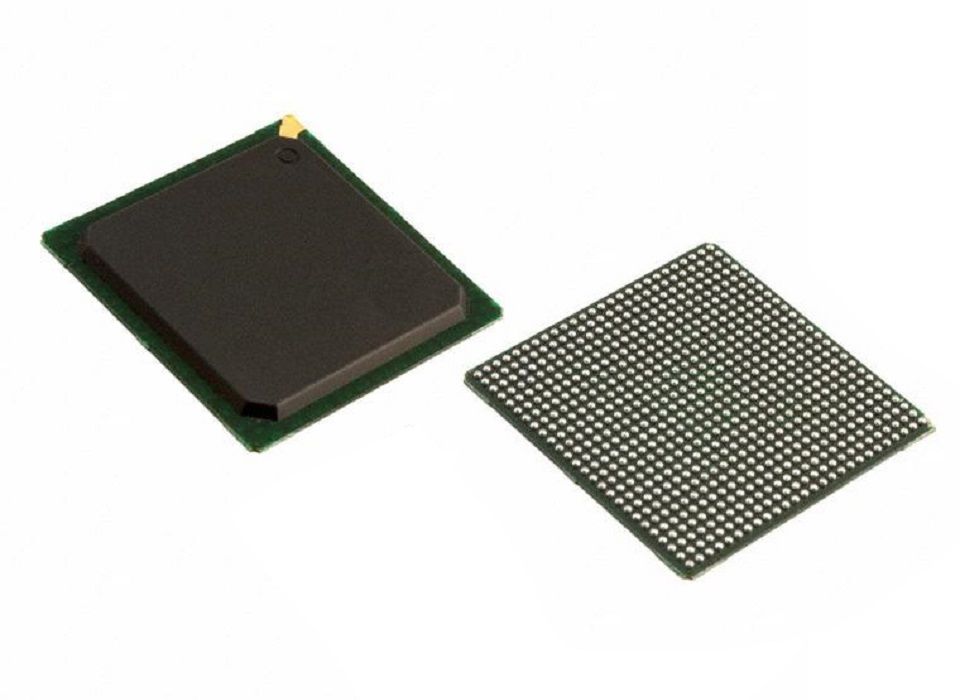

ПЛИС CSG484/FG484/FG676

Чип представляет собой ПЛИС (FPGA) на основе статической структуры памяти. Обладает большой емкостью и высокой производительностью.

Программируемая структура чипа состоит из следующих основных функциональных модулей: логический кластер (LC), внутренние коммутационные ресурсы, программируемый элемент ввода-вывода (IOE), PLL, DSP и BRAM.

Программируемая структура чипа состоит из следующих основных функциональных модулей: логический кластер (LC), внутренние коммутационные ресурсы, программируемый элемент ввода-вывода (IOE), PLL, DSP и BRAM.

Основные характеристики:

Основан на стандартном 40-нм процессе проектирования CMOS

Эффективная пропускная способность достигает 13,6 миллионов регистров

- 136000 4-входовая LUT;

- 136000 программируемых регистров;

- 1200 ячеек BRAM по 4,5 Кбит (включая биты четности), до 5400 Кбит двухпортовой ОЗУ;

- 192 множители 18 бит × 18 бит.

Высокоскоростное управление тактовой частотой для комплексной оптимизации энергопотребления, задержки, джиттера и перекоса

- 8 программируемых PLL для синтеза частоты;

- Максимальная частота управления тактовой частотой может достигать более 500 МГц;

- Обеспечивает до 16 глобальных тактовых сигналов.

Доступно до 498 программируемых пользовательских входов/выходов

- Поддержка различных стандартов ввода/вывода: 3,3 В/2,5 В/1,8 В/1,5 В - стандарт LVTTL/LVCMOS, поддержка SSTL2/SSTL3;

- Обеспечивает до 249 дифференциальных пар стандартов LVDS с максимальной скоростью передачи более 640 Мбит/с;

- Поддержка встроенного терминатора цифрового управления (Digital Control Impedence, DCI); Возможность программирования привода ввода-вывода, управление скоростью нарастания, удержание шины, слабая подтяжка и т. д.; Схема граничного сканирования, совместимая со стандартом IEEE 1149.1.

Применение различных конфигураций

- Поддержка Master Serial, Slave Serial, Master parallel, Slave parallel, JTAG (Joint Test Action Group) и другие методы конфигурации;

- Рекомендуемая частота конфигурации от 1 МГц до 15 МГц.

Уровень качества

- Используйте пластиковые корпусы FG484 / CSG484 для соответствия требованиям качества, обеспечивает 338 операций ввода-вывода, 169 пар дифференциальных пар LVDC, рабочий диапазон температур: -55℃ ~125℃;

- Используйте пластиковый корпус FG676 для обеспечения 498 операций ввода-вывода, 249 пар дифференциальных пар LVDC, температурный диапазон -55℃ ~125℃; выдерживаемое напряжение электростатическим разрядом более 2000 В.

Программируемая структура микросхемы в основном состоит из следующих функциональных модулей, как показано на рисунке 1:

- логический кластер (LC),

- внутренние ресурсы межсоединений,

- программируемый элемент ввода-вывода (IOE),

- PLL,

- DSP

- BRAM.

Основная схема устройства состоит из массива LC 164×100. LC является относительно независимым объектом, который может выполнять определенные логические функции самостоятельно или связываться друг с другом через каналы связи между LC для достижения более сложной логической функции.

Модуль ресурсов внутреннего соединения включает в себя канал соединения (далее именуемый «Отслеживание») и перекрестный коммутатор канала соединения (далее именуемый «Коммутатор»).

Канал соединения дополнительно делится на горизонтальный и вертикальный каналы соединения, которые состоят из набора обычных соединительных блоков и отвечают за реализацию соединения между блоками логической матрицы.

Логический массив окружен программируемыми блоками ввода-вывода, которые отвечают за связь между внутренними и периферийными схемами микросхемы. Чип может обеспечить до 498 программируемых пользователем вводов/выводов.

Чип обеспечивает независимый программируемый модуль PLL. Пользователи могут легко настроить PLL для выполнения таких функций, как синтез частоты, фазовый сдвиг и регулируемый рабочий цикл.

Чип обеспечивает 48 блоков цифровой обработки сигналов (DSP). Каждый блок DSP может одновременно выполнять восемь умножений 9b×9b, или четыре умножения 18b×18b, или одно умножение 36b×36b, а результат умножения может выполнять такие операции, как сложение, вычитание, накопление и суммирование. Каждый блок DSP содержит 18-битный входной регистр сдвига для обычных приложений цифровой обработки сигналов, таких как FIR, IIR и т. д.

Устройство имеет 1200 ячеек BRAM с общим объемом ОЗУ 5400 КБ, которые могут выполнять следующие функции: реализовывать различные функции хранения, такие как ОЗУ, ПЗУ, сдвиговый регистр и FIFO, для удовлетворения потребностей пользователя в различных формах памяти; реализовать различные режимы работы, включая режим порта (режим одного порта, режим двух портов) и режим часов (режим одиночных часов, режим часов чтения/записи, режим часов ввода/вывода и независимый режим часов); контроль входных и выходных сигналов, в том числе: регистрация входных и выходных сигналов, наглядная реализация; реализация байтового включения; настройка ширины слова; настройка режима чтения при записи; и т. д.

Кроме того, пользователь может инициализировать содержимое встроенной программируемой памяти (BRAM), запрограммировав информацию об инициализации.

Логический кластер(LC)

LC (Logic Cluster) — модуль логического массива в FPGA. Каждый LC содержит 10 BLE (базовых логических элементов) и 1 схему управляющей логики. BLE — это самый простой программируемый логический блок. Логическая схема управления отвечает за генерацию управляющих сигналов для каждого BLE в одном и том же LC. Базовая структура LC показана на рисунке 2.Сетевые часы

Чипы серии FPGA обеспечивают стабильный и быстрый тактовый сигнал, включая глобальные часы и региональные часы. Глобальный тактовый сигнал поступает с верхней, нижней, левой и правой сторон микросхемы. Всего через S0 в тактовую сеть вводится 32 тактовых сигнала.

Каждый квадрант имеет 16 тактовых сигналов и распределяется по каждой тактовой области ядра через 4 уровня модулей от S0 до S3. Reginalclock обеспечивает ввод со всего ядра чипа и входит в сеть часов через S3.

Функции, предоставляемые сетью часов, включают:

- Синхронный сброс тактового сигнала;

- Функция деления тактовой частоты, поддержка 2, 4, 6, 8 частотного деления;

- Функция Gated Clock, управляющий сигнал поступает от ресурсов канала;

- Обеспечение 8-канального сетевого интерфейса часов на ресурсах проводки канала; сигнал поступает от верхнего, нижнего, левого и правого iotrack;

- Область часов S3 обеспечивает часы в области максимум 32 * 32 BLK; каждый 4 * 4 BLK содержит закрытый буфер, управляющий часами модуля 4 * 4 BLK (должны быть включены или выключены). Часы выключены, чтобы уменьшить энергопотребление, когда они не используются;

- Обеспечение вывода часов из конечной точки сети часов.

Блок ввода и вывода

Блок ввода и вывода IOBLK (Input Output BLOCK) состоит из SwitchBox, ConnectionBox, управляющей логики и IOE:- SwitchBox реализует скачок сигнала между каналами и подключение входного/выходного сигнала к каналу;

- ConnectionBox реализует сигнал между каналом и логикой управления IOE Connection; логика управления генерирует различные управляющие сигналы для IOE;

- IOE реализует комбинированный/синхронный режим, прямой/обратный режим входного / выходного сигнала и разрешающего сигнала. IOE распределяется в IOBLK (блок ввода-вывода) вокруг микросхемы. Каждый верхний и нижний IOBLK содержит до 6 IOE. Столбец IOBLK может быть связан с вертикальным каналом, а ряд IOBLK может быть связан с горизонтальным, вертикальным или прямым каналом.

- Входной сигнал вывода ввода/вывода может быть введен в логическую матрицу через IOE. Выходной сигнал логического массива может быть выведен на контакт ввода-вывода через логику управления и IOE. Путь передачи сигнала показан на рисунке 5.

Модуль ввода-вывода IOE (элемент ввода-вывода) обеспечивает программируемый двунаправленный интерфейс для контактов ввода-вывода и внутренней логики.

Каждый IOE включает в себя входной регистр, выходной регистр и выходной разрешающий регистр для реализации регистрации входных / выходных данных и выходных разрешающих сигналов соответственно.

IOE может реализовать два режима быстрого комбинирования и общего ввода, где для входных и выходных сигналов реализованы прямой, обратный, комбинированный режим и режим синхронизации. В нормальном двунаправленном режиме работы входной сигнал может использоваться для удовлетворения требований к быстрому времени установления входного сигнала. Входной регистр имеет свой собственный вход и часы, независимые от выходных и выходных регистров разрешения.

Выходной регистр может использоваться для удовлетворения требований быстрого вывода тактовых импульсов. Регистр включения вывода и регистр вывода совместно используют одни и те же часы и сигнал включения часов. Все регистры также могут выполнять синхронную / асинхронную функцию PRSET / CLEAR или без функций, при включении питания (POWERUP), с активным низким уровнем (0: включение) или с активным высоким уровнем (1: включение).

BRAM

Чип включает в себя 1200 независимо программируемых 4,5 Кбит BRAM (Block RAM), которые могут реализовывать до 1728 Кбит программируемых ресурсов встроенной памяти.- Размер каждого массива хранения BRAM составляет 128 × 36;

- Поддерживаемые режимы портов: упакованный, один порт, простой двойной порт и настоящий двойной порт;

- Поддерживаемые режимы обработки конфликтов чтения-записи: чтение в первую очередь и запись в первую очередь.

- Поддерживаемые режимы ширины слова: 1, 2, 4, 8, 9, 16, 18, 32, 36;

- Поддерживаемые режимы часов: одиночные часы, часы чтения-записи, часы ввода-вывода и независимые часы;

- Поддержка байтовой функции включения входных данных;

- Поддержка функции очистки входного сигнала;

- Поддержка функции очистки регистров при включении питания;

- Поддержка синхронного и асинхронного выбора выходных данных;

- Поддержка функции обратного чтения при инициализации.

Цифровая обработка сигналов (DSP)

Модуль DSP поддерживает пять типов арифметических операций: умножение, сложение, вычитание, накопление и суммирование. Эти виды операций могут удовлетворить большинство функций цифровой обработки сигналов, таких как FIR, IIR, FFT, DCT и другие алгоритмы.Модуль DSP может одновременно выполнять:

- Восемь множителей 9 × 9 бит

- Четыре множителя 18 × 18 бит

- Один множитель 36 × 36 бит

Модуль DSP состоит из следующих основных блоков:

- блок умножения

- сумматор / вычитатель

- аккумулятор / сумматор

- блок вывода

- выходной регистр

JTAG-схема

Схема JTAG — это особая структура схемы, добавленная для достижения совместимости с протоколом IEEE 1149.1-2001. Его функция заключается в выполнении различных обязательных функций, указанных в протоколе IEEE 1149.1-2001, и некоторых дополнительных функций. Он поддерживает протокол JTAG и имеет функцию тестирования граничного сканирования.Граничное сканирование — это метод тестирования структуры, который добавляет регистры к порту ввода-вывода микросхемы и в тестовом режиме может быть подключен как канал граничного сканирования. Тест граничного сканирования может выполнять тест межсоединений на уровне платы путем захвата, предварительной загрузки, фиксации и других функций значений контактов ввода-вывода через специальный интерфейс JTAG.

Схема JTAG состоит из семи модулей:

- TAP-контроллера,

- регистра инструкций и его логики принятия решений,

- регистра граничного сканирования,

- регистра обхода,

- регистра идентификатора устройства,

- регистра конфигурации

- регистра BitProbe.

Структура схемы системы показана на рисунке 6.